#### Bosch IP TechDay 2024 GTM Technical Overview

(h)

BOSCH

ME-IC/PRM-IP | March 15th, 2024

**GTM-IP**

Agenda

- 2. Infrastructure Module

- 3. I/O Modules

- 4. Special Function Module

- **5.** Safety Module

6. Core Module

BOSCH

## GTM Introduction

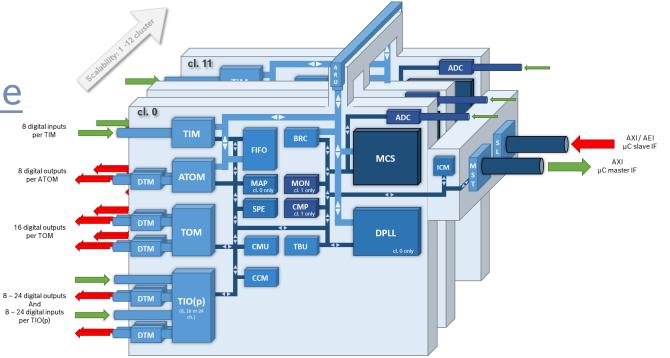

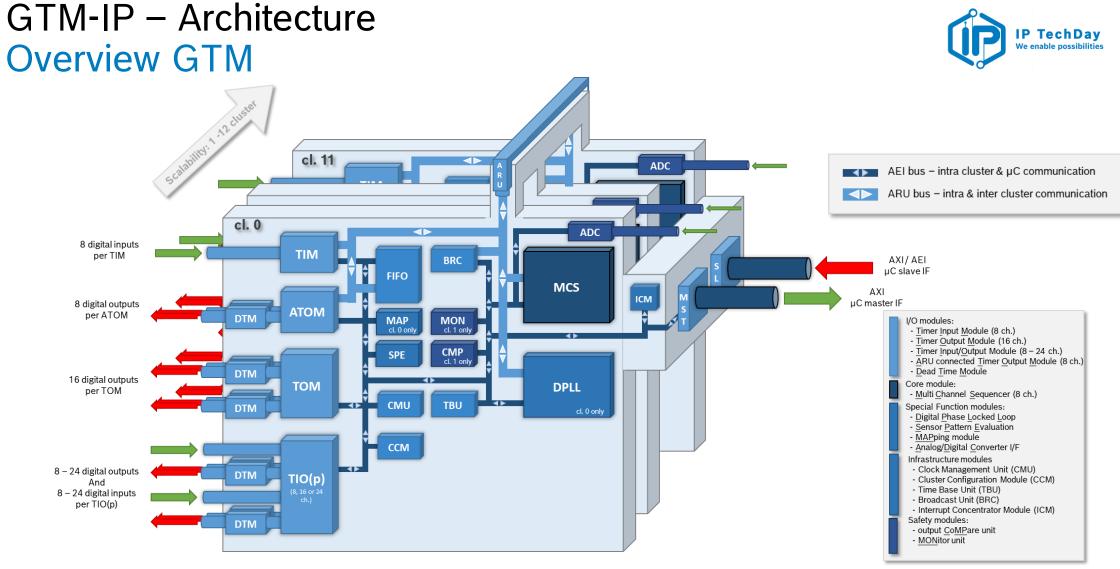

#### GTM-IP – Architecture What is GTM (Generic Timer Module)?

- Offloading real-time critical I/O workloads from µC cores to a specialized I/O co-processor with massive parallel thread handling capabilities

- Common architecture across multiple semiconductors

- Development of software/applications independent of selected MCU

- Scalable design approach

- Scales with the application demand from low-end to high-end class

- Generic architecture

- Covering a wide range of application domains (powertrain, traction control, chassis control, xEV, inverter, PFC, industry, ...)

- Open to 3rd parties to contribute to nextGen requirements

- Growing Eco-Environment

- Enables development of a rich set of tools and compilers

## GTM Infrastructure Modules

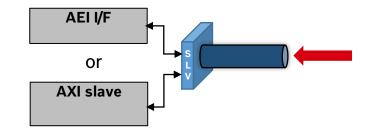

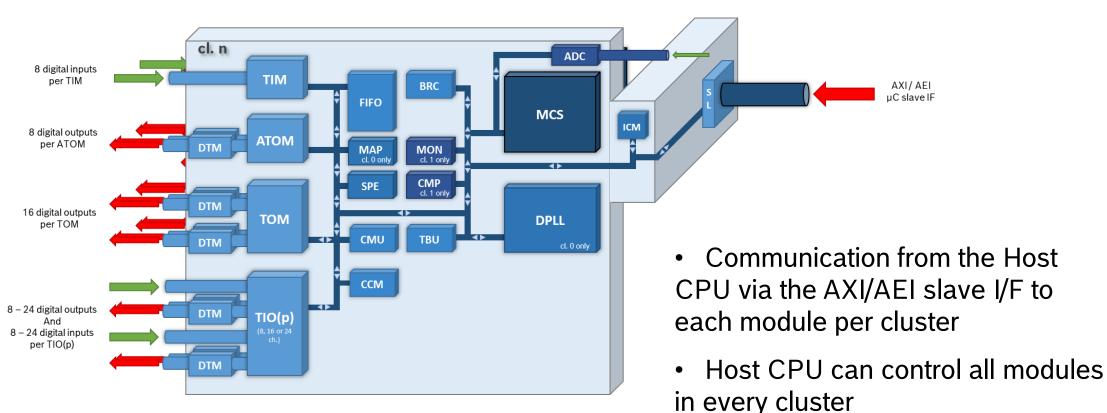

#### GTM-IP – Architecture µC to GTM interface [AEI or AXI slave]

μC to GTM interface [AEI or AXI <u>slave]</u>

Primary access path from  $\mu$ C bus masters (usually  $\mu$ C cores) to GTM resources

- The GTM-IP is equipped with 2 slave Interfaces

- a generic bus interface AE Interface (AEI)

- a AXI slave, Full AMBA AXI 3.0 compliant)

- Via the slave I/F all modules in the GTM can be controlled/configured in each cluster

Note: Only one of the two  $\mu$ C slave interfaces is available depending to device configuration.

> AEI = Automotive Electronics Interface AXI = Advanced eXtensible Interface

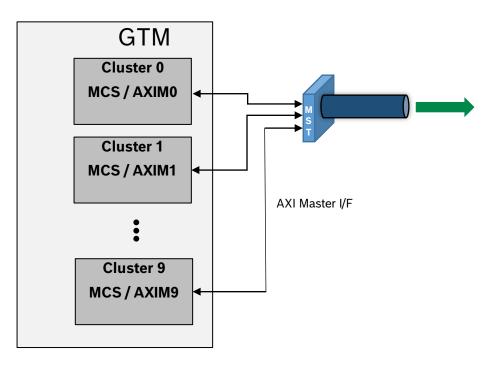

#### GTM-IP – Architecture GTM to µC interface [AXI master]

GTM to µC interface [AXI master]

GTM bus master interfaces; enables MCS to access/control  $\mu$ C resources outside GTM

- AXI master (Full AMBA AXI 3.0 compliant)

- the GTM MCS

8

- Max 10 MCS / AXI master

- The MCS (Multi Channel Sequencer) Core can control via the AXI master peripherals/memory on the Soc

- Depending on the implementation by the integrator

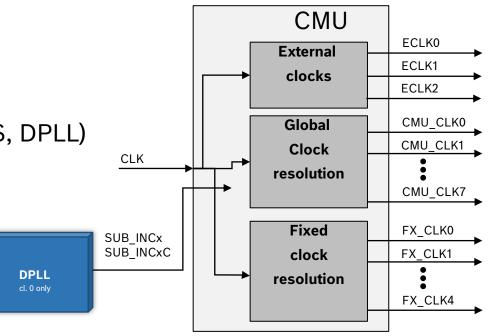

## GTM-IP – Architecture CMU - Clock Management Unit

- The Clock Management Unit (CMU) enables/generated the 14 clock sources of the GTM

- External clock

- External of GTM

- Clock resolution (Timer resolution)

- Global (TIM, ATOM, TBU, TIO, DTM, MCS, DPLL)

- SW conf dividers

- Fixed (TOM only)

- 5 fixed dividers

• The CMU is only available in cluster 0.

© Robert Bosch GmbH 2024. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

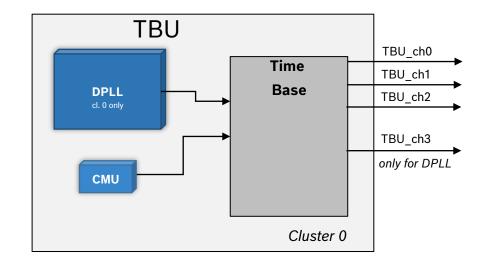

#### GTM-IP – Architecture TBU - Time Base Unit

<u>Time Base Unit</u> Multi-channel timebase unit. Provides multiple timebases for GTM resources

- The Time Base Unit TBU provides common time bases for the GTM-IP.

- Organized in channels

- number of channels is device dependent

- up to four channels

- There are 3 modes:

- Free Running Counter Mode

- Forward/Backward Counter Mode

- Modulo Counter Mode

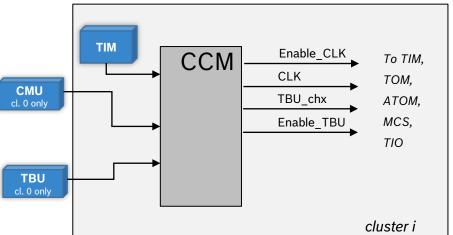

#### GTM-IP – Architecture CCM - Cluster Configuration Module

- The Cluster Configuration Module (CCM) enables the configuration of several cluster specific options namely:

- cluster's clock frequency

- module clock gating

- status observation of the cluster's MCS bus master (AEM),

- address range protection

- global architecture configuration

- TIM input as clock resolution

<u>Cluster Configuration Module</u> Cluster Infrastructure module and configuration management

Only showed the CCM clk and gating functions

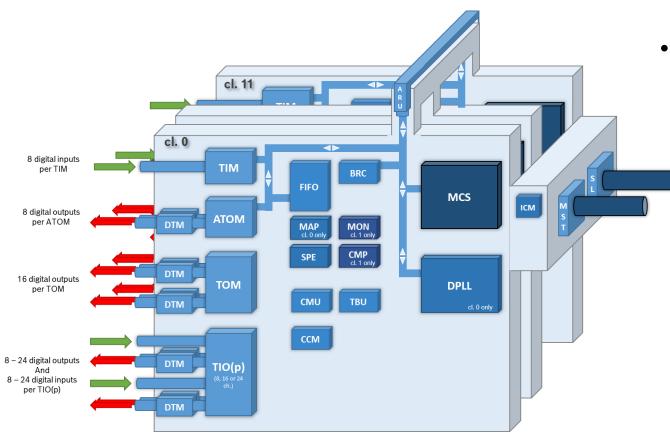

#### GTM-IP – Architecture AEI Bus inside each cluster Intra cluster communication

**AEI (AE Interface) Bus**

GTM communication path inside a cluster for all modules from the slave AXI/AEI I/F

#### Only AEI bus shown in one cluster

© Robert Bosch GmbH 2024. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

#### GTM-IP – Architecture ARU - Advanced Routing Unit Intra and Inter cluster communication

<u>Advanced Routing Unit</u> GTM communication path for ARU-connected modules. Intra- and inter-cluster communication

- The Advanced Routing Unit offers:

- Intra cluster communication

- Inter cluster communication

- For the TIM / ATOM / BRC / DPLL / MCS and FIFO

© Robert Bosch GmbH 2024. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

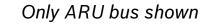

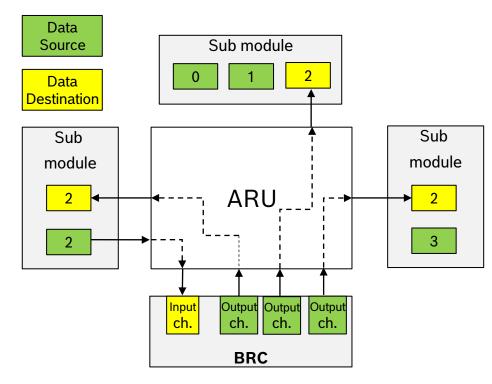

#### GTM-IP – Architecture ARU - Advanced Routing Unit

- The ARU (Advanced Routing Unit) provides a flexible and resource efficient way for connecting any data source to an arbitrary data destination inside the GTM

- Intra cluster communication

- Inter cluster communication

- P2P (Point to Point) connection

#### Advanced Routing Unit

GTM communication path for ARU-connected modules. Intra- and inter-cluster communication

ARU data routing principle.

#### GTM-IP – Architecture BRC - BRoadCast Unit

• The Broadcast (BRC) enables duplication of data streams (output of modules) to multiple destination (different input channel of modules)

• The BRC submodule provides 12 input channels as well as 22 output channels.

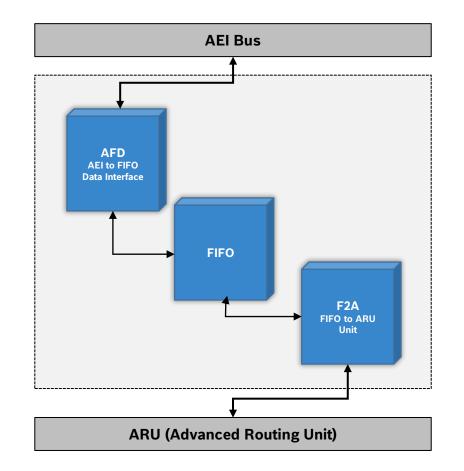

### GTM-IP – Architecture FIFO – First In First Out Unit

FIFO Unit

ARU connected FIFO memory

- Application usage:

- store data in the GTM and send data out of the GTM.

- F2A (FIFO to ARU unit)

- Interface of the FIFO to the ARU bus

- AFD (AEI to FIFO Data Interface)

- interface of the FIFO to the AEI bus.

# GTM 4.1 I/O Modules

## GTM-IP – Architecture Overview – Timer Units

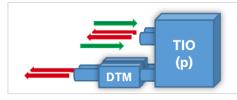

- TIO Timer Input Output Module

- Low-complexity Timer for PWM, filtering and serial shift

- TIM Timer Input Modules

- Filtering and capturing of input signals e.g.

- Timeout Detection / Input Edge Counter

- Signal Measurement (PWM duration)

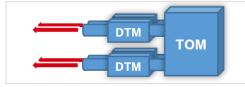

- TOM Timer Output module

- Generate PWM Signals

- ATOM ARU connected TOM

- Able to generate complex waveforms

- Dead Time:

- Change of output signal

<u>Timer Input Output Module</u> 8 to 24 I/O channels w/ capture incl. basic input filters) (p) = plus (increment/decrement/compare/shift)

<u>Timer Input Module</u> 8 channels of complex capture & compare functions (incl. input filters)

Timer Output Module

16 channels of complex output waveform generation (PWMs)

<u>ARU connected Timer Output Module</u> 8 channel advanced TOM functionality

<u>D</u>ead <u>T</u>ime <u>M</u>odule

Support for delayed, inverted or duplicated output signals including cross-channel combinatorial postprocessing of output signals

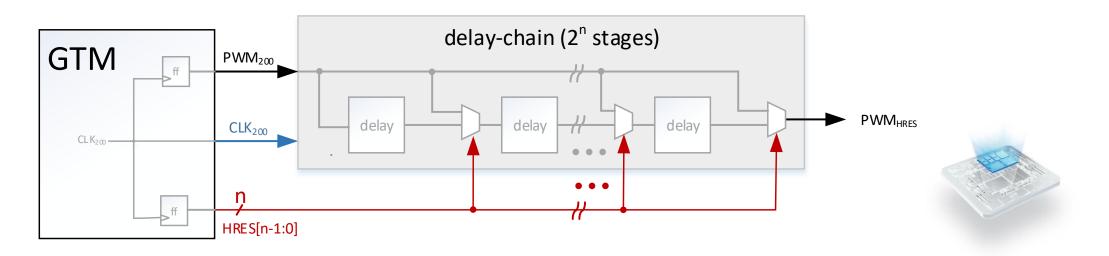

#### GTM-IP – Architecture HighRes

- Support for HighRes PWM generation

- Generating PWM at resolutions up to 156.2 ps (GTM @ 200 MHz; n = 5) with external delay chain solution

## GTM Special Function modules

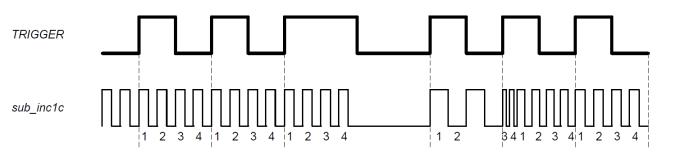

#### GTM-IP – Architecture DPLL Digital Phase Locked Loop

DPLL cl. 0 only <u>Digital Phase Locked Loop</u>

Engine positioning management including high resolution angle clock base and dynamic scheduling of trigger events

- The digital PLL Phase Locked Loop (DPLL) submodule is used for frequency multiplication.

- Application Usage:

- Calculation of the position information of linear or angular motions, mass flow values, temperature, pressure or level of liquids, for example engine positioning detection and signaling (angle clock).

- Example for four times higher frequency:

- DPPL is configured to generate 4 micro ticks [sub\_inc1c (output of DPLL)] per tick from Trigger (input of DPLL) (Tick is from rising edge to rising edge)

21

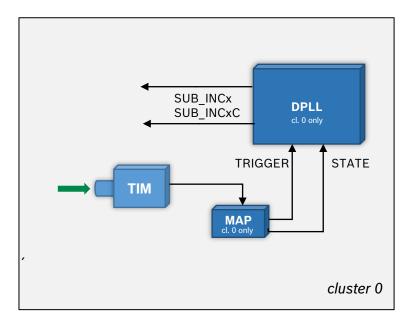

#### GTM-IP – Architecture MAP - MAPing module

- The MAP Mapping submodule generates the two input signals TRIGGER and STATE for the submodule DPLL by evaluating the output signals of the channel 0 up to channel 5 of submodule TIMO (only cluster 0).

- By using the TIM as input submodule, the filtering of the input signals can be done inside the TIM channels themselves.

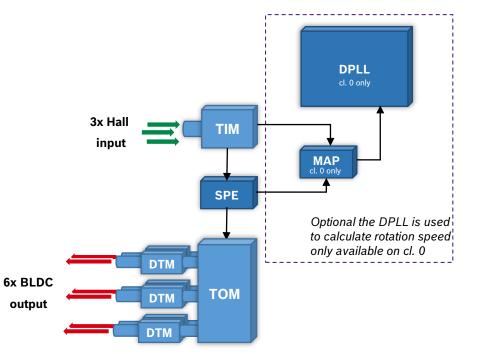

#### GTM-IP – Architecture SPE – Sensor Pattern Evaluation Unit

The Sensor Pattern Evaluation (SPE) submodule can be used to evaluate three hall sensor inputs and together with the TOM module to support the drive of BLDC (Brush-Less DC) motors.

Input signals are filtered already in the connected TIM channels.

SPE

## GTM Safety modules

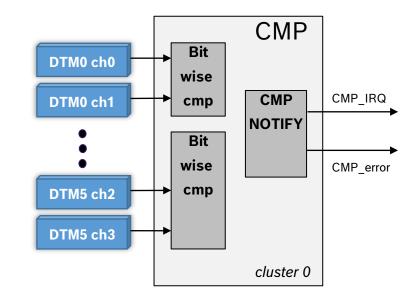

#### GTM-IP – Architecture CMP - CoMPare Unit

• Application usage:

Comparing duplicate outputs

- The CMP submodule can compare two adjacent channel outputs from TOM or ATOM submodules and raises an error, when the two signals are not identical.

- max 2x24 ch

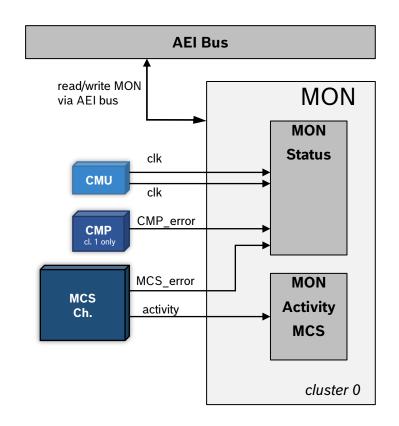

#### GTM-IP – Architecture MON - MONitor Unit

- The MON submodule monitors the GTM internal clocks and the MCS functionality.

- the activity of the clocks is supervised

- No activity leads to Safety INT

- Characteristics of signals can be checked in MCS

- the ARU cycle time can be compared in a MCS channel to given values

## GTM Core module

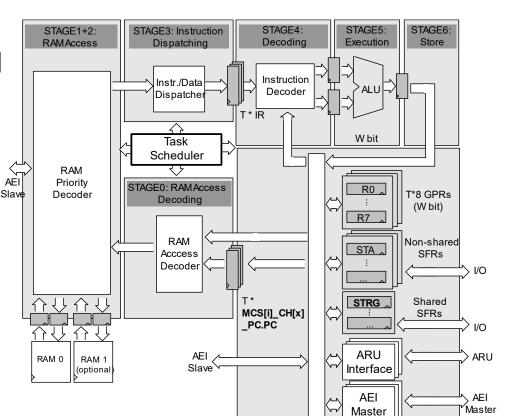

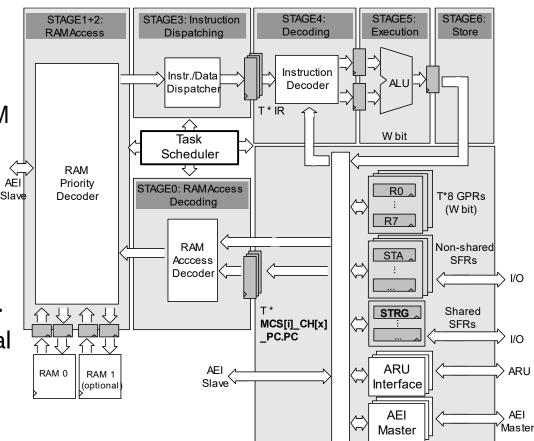

#### GTM-IP – Architecture MCS - Multi Channel Sequencer

- The MCS is a 24bit instruction RISC (Reduced Instruction Set Compute) CPU core with 8 parallel threads

- Determistic, every 9<sup>th</sup> cycle 1 thread is executed

- Control/monitor internal GTM signals and external modules on the Soc/µC

- Master for all modules in a cluster

- MCS has priority over slave I/F AEI or AXI

- Every 9<sup>th</sup> cycle is reserved for slave I/F AEI or AXI

- MCS can be stopped for bus access

- ARU connection to other cluster.

**Multi Channel Sequencer**

8 parallel threads

real-time optimized RISC cores with

MCS

#### GTM-IP – Architecture MCS - Multi Channel Sequencer

- Application usage:

- is to calculate complex output sequences that may depend on the time base values of the TBU and are processed in combination with the ATOM submodule

- to perform extended data processing of input data resulting, e.g. from the TIM submodule

- process data provided by the CPU within the MCS submodule, and the calculated results are sent to the outputs using the ATOM submodules.

- E.g. thread waits for condition of an SFR (Special Function register) or time base value

- SFR can change with an INT from a module (e.g. TIM)

MCS

Juergen Hanisch Gregor Sunderdiek